COMMONWEALTH

OF AUSTRALIA

# DEPARTMENT OF SUPPLY AUSTRALIAN DEFENCE SCIENTIFIC SERVICE AERONAUTICAL RESEARCH LABORATORIES

Mechanical Engineering Report 126

# A DATA ACQUISITION SYSTEM SUITABLE FOR AIRBORNE APPLICATIONS

by

K. F. FRASER

MELBOURNE

July 1969

#### DEPARTMENT OF SUPPLY

#### AUSTRALIAN DEFENCE SCIENTIFIC SERVICE

#### AERONAUTICAL RESEARCH LABORATORIES

MECHANICAL ENGINEERING REPORT 126

# A DATA ACQUISITON SYSTEM SUITABLE FOR AIRBORNE APPLICATIONS

by

K. F. FRASER

#### SUMMARY

Techniques applicable to airborne data acquisition and recording are reviewed. From this review a system which allows simultaneous recording of analogue and digital data with a single analogue tape machine has been designed conceptually. Such a system offers many advantages over the other systems available for airborne data recording in Australia.

The system will accommodate with appropriate accuracy most data acquisition and recording requirements which arise in the testing of aircraft by the Aeronautical Research Laboratories. Simultaneous recording of flight crew commentaries on the same magnetic tape recorder is readily performed. Analysis of the recorded data requires the use of analogue replay equipment in conjunction with a digital computer.

#### CONTENTS

|                                                                                   | Page No.       |

|-----------------------------------------------------------------------------------|----------------|

| INTRODUCTION                                                                      | 4              |

| PART A REVIEW OF TECHNIQUES APPLICABLE TO AIRBORNE DATA ACQUISITION AND RECORDING | 5              |

| A1. TECHNIQUES FOR RECORDING DATA ON MAGNETIC TAPE                                | 5              |

| A1.1. Direct                                                                      | 5              |

| A1.2. Carrier Erase                                                               | 6              |

| A1.3. Frequency Modulation                                                        | 6              |

| A1.4. Pulse Duration Modulation                                                   | 7              |

| A1.5. Pulse Code Modulation                                                       | 9              |

| A1.6. Comparison of Recording Techniques                                          | 10             |

| A2. TECHNIQUES SUITABLE FOR USE IN AIRBORNE DATA RECORDING                        | 12             |

| A3. SIGNAL CONDITIONING REQUIREMENTS RELEVANT TO AIRBORNE RECORDING               | <b>DATA</b> 13 |

| A3.1. Transducers and Associated Signal Conditioning Equipment                    | 13             |

| A3.2. Power Supplies for Signal Conditioning Equipment                            | 17             |

| PART B REQUIREMENTS FOR A HYBRID RECORDING SYSTEM                                 | 17             |

| B1. ANALOGUE RECORD SYSTEM EXTENSIONS                                             | 17             |

| B1.1. Recording of Reference Frequencies                                          | 18             |

| B1.2. Improvement in Signal to Noise Ratio in the FM Recording System             | 19             |

| B1.3. PDM System Requirements                                                     | 19             |

| B2. PROPOSAL FOR A DIGITAL RECORDING SYSTEM                                       | 21             |

| B2.1. Tape Recorder Requirements                                                  | 21             |

| B2.2. Digital Data Acquisition Equipment Requirements                             | 22             |

| B2.3. Proposed Record Format                                                      | 23             |

| B2.4. System Detail                                                               | 24             |

| B2.4.1. Multiplexer                                                               | 24             |

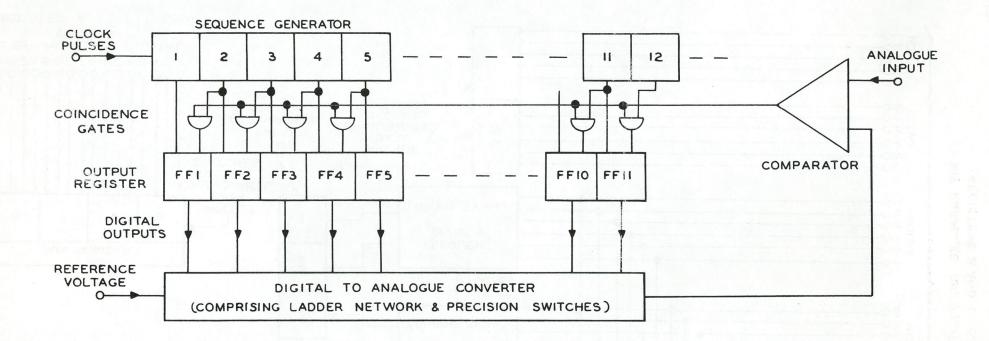

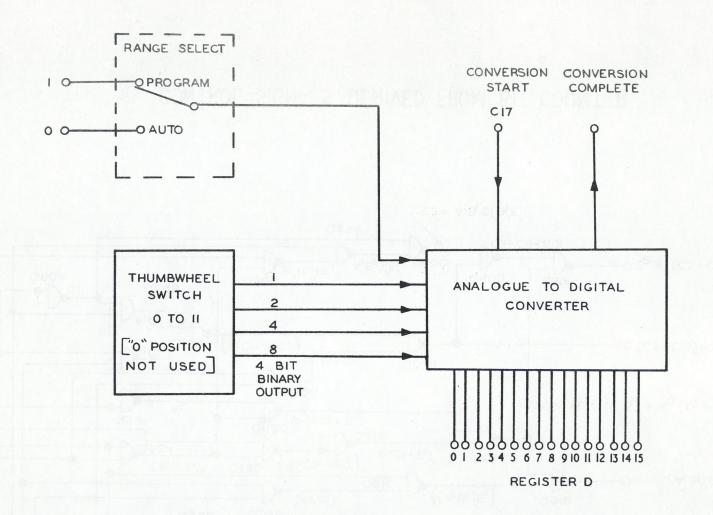

| B2.4.2. Analogue to Digital Converter                                             | 26             |

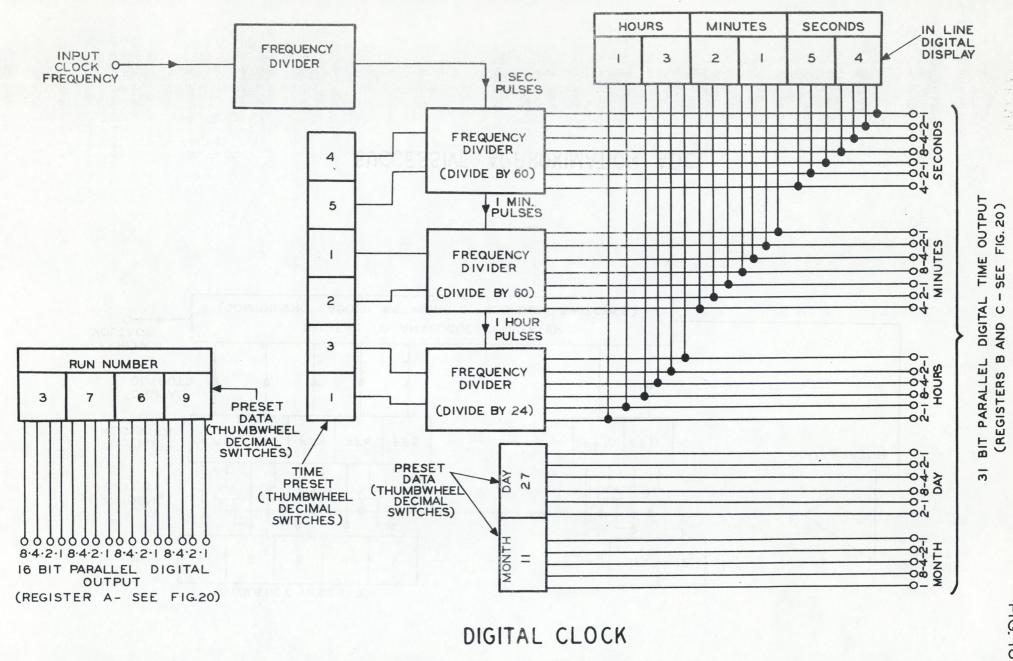

| B2.4.3. Digital Clock                                                             | 28             |

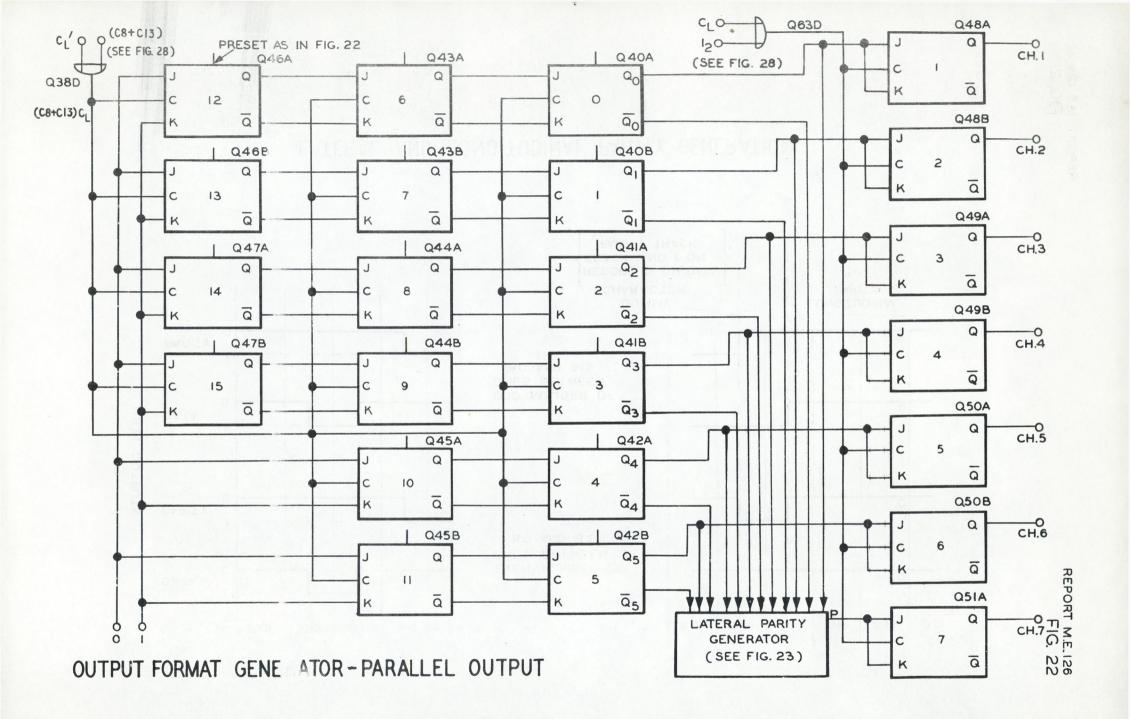

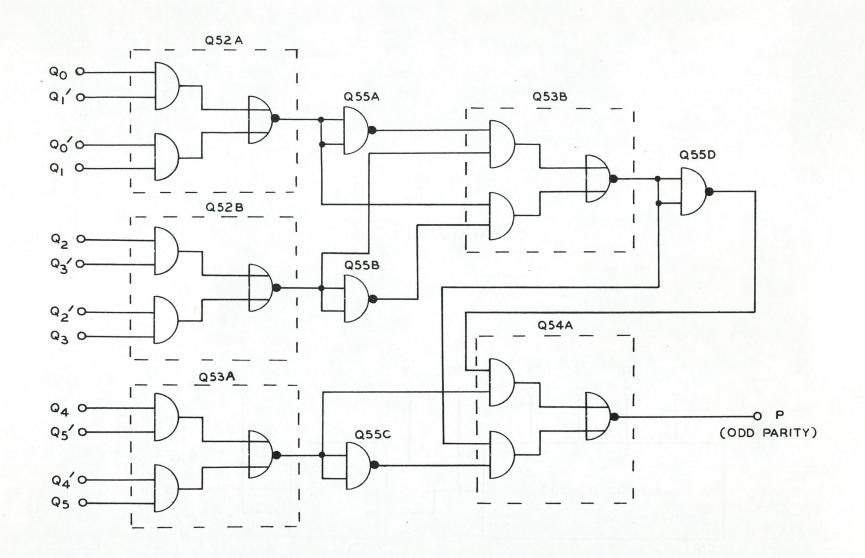

| B2.4.4. Output Format Generator | 29 |

|---------------------------------|----|

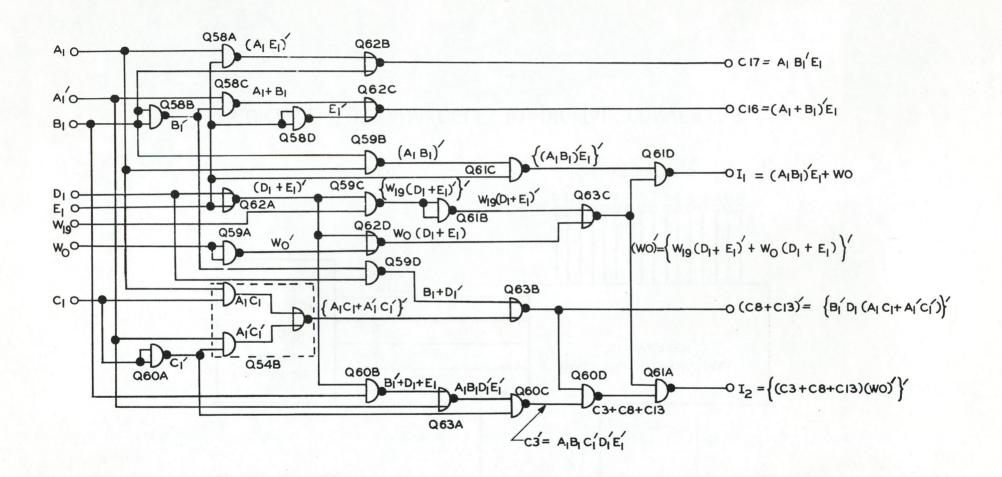

| B2.4.5. Programmer              | 32 |

| B2.4.6. Record Head Amplifiers  | 30 |

| B3. MONITOR FACILITY            | 31 |

| B4. PROPOSAL FOR DATA REDUCTION | 38 |

| CONCLUSION                      | 39 |

| REFERENCES                      | 41 |

| APPENDIX                        | 43 |

| FIGURES                         |    |

#### INTRODUCTION

In-flight data acquisition is an essential requirement for aircraft performance studies. With the many recent advances in magnetic tape handling equipment and computers it has become advantageous to store the acquired data on magnetic tapes. Detailed analysis of the data is usually performed later at a suitable ground station.

The magnetic tape recording instrument may be installed in the aircraft or may be situated at a ground station. In the latter instance radio telemetering of the data from the aircraft to the ground station is required. Generally the radio telemetering system is only applicable when the aircraft under study is in the vicinity of the ground station. The cost of the telemetering system tends to be prohibitive except for large scale research. If the magnetic tape recorder is installed in the aircraft it must be specially engineered to operate in the aircraft environment. A range of airborne magnetic tape recorders is now commercially available.

Aircraft evaluation studies involve the measurement of many physical quantities. Some quantities such as vibration displacement, noise and pressures at various points in jet engines are not normally required to be measured with extreme accuracy but frequently involve measurement over large bandwidths. Such data is usually recorded using analogue techniques. Other quantities such as airspeed, altitude, air temperature and engine speed frequently have to be measured with very high precision but usually over a relatively small bandwidth. High precision is required to enable basic computed quantities such as Mach Number and True Air Speed to be accurately evaluated and to enable small changes in performance to be indicated. Digital techniques must be employed for the recording of such data to the desired accuracy. Fortunately, in aircraft studies, large bandwidth and high precision are very rarely required simultaneously in a given measurement.

Magnetic tape recorders have been developed to a high degree of sophistication in both the analogue and the digital fields. However, the recorders have tended to be developed along different lines as the requirements are somewhat conflicting. Hence magnetic recorders are usually referred to as "analogue" or "digital." Generally analogue recorders require large recording bandwidths, good linearity, wide dynamic range and low crosstalk between channels. Staggered heads are invariably used to enable crosstalk between channels to be reduced sufficiently. Digital recorders, on the other hand, are usually designed to accept parallel data which, for high data packing densities, places very stringent requirements on azimuth alignment of the data on the tape. Invariably, digital recorders employ a single in-line headstack.

The trend to use separate machines for analogue and digital recording has been largely followed in aircraft studies. Larger aircraft can readily accommodate separate machines to record analogue and digital data. However, space limitations on many smaller aircraft, particularly military types, frequently do not allow the installation of separate recorders. In view of this latter application the concept of a "hybrid" recorder has evolved. The "hybrid" recorder is an analogue type recorder capable of simultaneously recording analogue and digital data.

This paper has been divided into two sections.

Section A is a review of the techniques applicable to airborne data acquisition and recording. From this review the need for simultaneous analogue and digital recording is established.

Section B relates to the hybrid recording system. Possible extensions of the analogue system of recording are indicated and a complete proposal for a digital recording system is given. The problems introduced when digital recording is performed on an analogue machine are described and analysed. Programme control requirements are developed and the logical sequences are derived for the digital system.

A scheme for seven channel parallel digital recording of data using the same analogue tape machine as used for the hybrid recording is also presented in Part B. For special applications in which only digital data is required such a system may be very useful.

# PART A REVIEW OF TECHNIQUES APPLICABLE TO AIRBORNE DATA ACQUISITION AND RECORDING

#### A1. TECHNIQUES FOR RECORDING DATA ON MAGNETIC TAPE

There are five main systems of recording data on tape which will be considered, namely:

- (1) Direct

- (2) Carrier Erase

- (3) Frequency Modulation

- (4) Pulse Duration Modulation

- (5) Pulse Code Modulation

The first four of these systems may be generally classified as "analogue" and the fifth system as "digital." The choice of a suitable recording system for each particular application will depend on the nature of the data to be recorded and the required accuracy. The characteristics of these systems of recording are detailed below.

#### A1.1. Direct

In this system the signal to be recorded is suitably amplified and mixed with a high frequency bias signal (Eldridge¹ and Bauer²). The combined signal is presented directly to the record head as a varying electrical current. The remanent flux density left on the tape is proportional to the magnitude of the signal current at the moment the tape passes the trailing edge of the record gap. Since the output from conventional reproduce heads is proportional to the rate of change of flux, DC data cannot be reproduced in the direct recording system. The practical lower frequency limit is approximately 50 hertz. The direct recording process has the advantage of providing the widest possible frequency range for any tape speed (Weber³). The limitations on the frequency response in direct recording are discussed by Danial, Axon and Frost,⁴, Martin⁵ and Borwick.⁶

The chief disadvantages of the direct recording system are:

- (i) Recording of frequencies below about 50 hertz is not feasible.

- (ii) Tape drop-outs which show up as loss of data or amplitude fluctuations seriously degrade the fidelity of the data recording. The effect is more serious at the higher recording frequencies. Franck<sup>7</sup> and Noble<sup>8</sup> discuss tape drop-outs in detail.

- (iii) The dynamic range is relatively small (25 db for the Ampex Model AR 200 Airborne Analogue Tape Recorder available at these laboratories), particularly for the small track widths used in multi-channel data recording. Camras<sup>9</sup> shows that the noise varies as the square root of the track width whereas the signal level changes directly as the track width. Hence reducing a track width to half size reduces the signal to noise ratio by 3 db. Noise is inherent in the magnetic recording process and cannot be eliminated. For further details on tape noise refer to Howling,<sup>10</sup> Snow<sup>11</sup> and Moris.<sup>12</sup>

- (iv) Crosstalk between adjacent channels becomes quite high as the recorded wavelengths are increased (16 db at 110 hertz and 60 inches per second [ips] for the Ampex Model AR 200 Tape Recorder).

- (v) The overall accuracy attainable is fairly low. An accuracy of 5% can be achieved but 10% is probably a more realistic figure.

- (vi) Godinez and Muench,<sup>13</sup> and Wainwright,<sup>14</sup> show that the direct recording technique produces considerable phase distortion unless special corrections are made. The problem of phase distortion arises because of the nature of the head plus tape characteristic. The replay head senses the rate of change of flux and hence the amplitude characteristic has a 6 db per octave upward slope. When the wavelength on the tape approaches the width of the reproduce head gap the replay amplitude starts to decrease. However, this drop in amplitude is not accompanied by a phase shift. When compensation (using linear networks) is used on replay to compensate for this "gap effect" phase shifts are introduced which produce phase distortion. Various systems of phase correction as indicated by Godinez and Muench,<sup>13</sup> and Wainwright,<sup>14</sup> can be employed.

Most instrumentation recorders (as distinct from audio recorders) provide a record characteristic (record head current versus frequency) which is flat over the specified frequency band. In contrast most audio recorders pre-emphasize the high frequencies, and sometimes the low frequencies, prior to recording. Such pre-emphasis is quite permissible in audio recorders where it can be assumed that components at the extremes of the audio band will always be of relatively low level. Because of the pre-emphasis audio recorders frequently have better specifications with respect to frequency response and signal to noise ratio than instrumentation recorders operated at the same speed.

#### A1.2. Carrier Erase

The carrier erase system of recording, discussed by Work and Lewis, 15 is a slight modification of the direct recording system. Prior to the acquisition of data a carrier is recorded on the tape and during acquisition the data signal erases a portion of the pre-recorded carrier. An amplitude modulated signal appears on the replay head. Usually the carrier is recorded at sufficient amplitude to saturate the tape. The erase curve is not completely linear but it is possible to choose a fairly linear portion for the operating range. DC bias is applied during the recording of the data so as to place the operating point centrally on the linear portion of the erase curve. To re-establish the data signal on replay an amplitude demodulator is required.

The carrier erase system is subject to the limitations associated with the direct recording system except that bandwidth is traded for the ability to record down to DC. The maximum data frequency is limited to approximately one-sixth of the carrier frequency. Bandwidths obtainable are comparable with those achieved using wideband frequency modulation (FM) recording techniques. Amplitudes in the carrier erase system are not affected by noise and tape speed variations to the same extent as in the FM system. In other respects the performance is inferior to wideband FM recording, accuracies no better than 5 to 10% being obtainable.

#### A1.3. Frequency Modulation

There are two main systems of frequency modulation (FM) recording in common usage, the wideband system and the narrow band system (IRIG16 and Godinez17). In the wideband FM recording system the chosen carrier is deviated by the modulating signal up to  $\pm 40\%$  of the carrier frequency whereas in the narrow band system the carrier is deviated up to  $\pm 7.5\%$  of the carrier frequency (±15% is also sometimes used). The FM recording technique overcomes the two basic limitations of the direct recording process namely the inability to record down to DC and the amplitude instability caused by tape drop-outs. The problem of phase distortion which arises in the direct recording system is absent in the FM recording system as the nonlinear phase characteristic of the tape recorder is not significant (Godinez and Muench<sup>15</sup>).

Tape speed variations are generally referred to as "wow" and "flutter" where "wow" refers to variations of a few hertz or less and "flutter" refers to variations at a higher frequency. The variations show up as noise on the replay channel (Godinez, 18 Disbray 19 and Pear 20) and hence it is imperative that they be kept to a minimum for FM recording. In the wideband system a 1% deviation in frequency resulting from flutter and wow in the tape transport would appear as a 100/40 = 2.5% noise signal, whereas in the narrow band system the corresponding noise signal would be  $100/7 \cdot 5 = 13 \cdot 3\%$

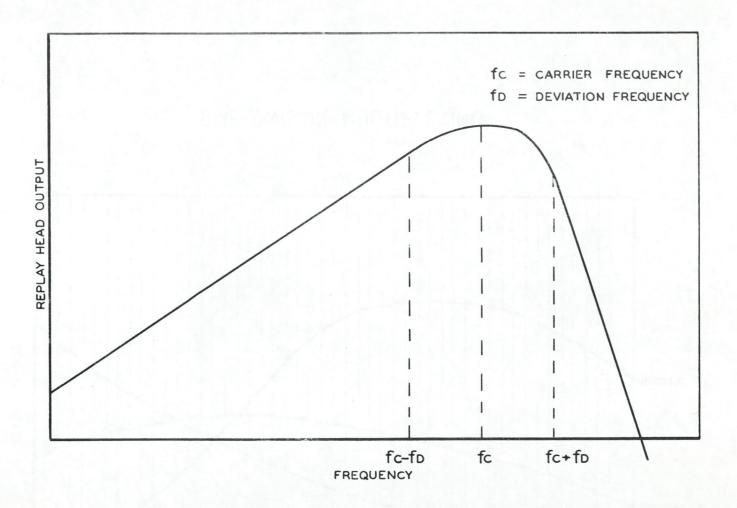

Normally the carrier frequency is placed at approximately the peak of the head to tape response curve (Fig. 1). Under these conditions, if the noise resulting from flutter and wow is neglected, the carrier can be reproduced fairly easily with a 40 db signal to noise ratio. Godinez<sup>21, 22</sup> shows that an analytical relationship exists between the signal to noise ratio of the FM carrier and the signal to noise ratio of the demodulated FM data.

For extended bandwidth operation  $\beta \simeq 2$ .

$$\left(\frac{S}{N}\right)_{\substack{\text{DEMOD.} \\ \text{FM}}} = 12\left(\frac{S}{N}\right)_{\text{CARRIER}}$$

That is a 12 times improvement in signal to noise ratio (once again neglecting the effects of flutter and wow).

At  $\beta$ 's less than 0.57 the signal to noise ratio of the FM data will be lower than the signal to noise ratio of the carrier.

Godinez<sup>22</sup> shows that greatly extended bandwidth FM may be achieved at the expense of reduced signal to noise ratio if micro-gap reproduce heads (30 micro inch say) are used and if the carrier is placed beyond the peak of the head to tape response (say at the 20 db down point). The table below shows a comparison between the standard IRIG system and the extended bandwidth system referred to above.

|            |         | IRIG FM   |                             | Exter   | nded Bandwidt | h FM                        |

|------------|---------|-----------|-----------------------------|---------|---------------|-----------------------------|

| Tape Speed | Carrier | Bandwidth | Signal to<br>Noise<br>Ratio | Carrier | Bandwidth     | Signal to<br>Noise<br>Ratio |

| 30 ips     | 27 KHz  | 0–5 KHz   | 42 db                       | 225 KHz | 0–100 KHz     | 30 db                       |

| 60 ips     | 54 KHz  | 0–10 KHz  | 42 db                       | 450 KHz | 0–200 KHz     | 30 db                       |

In the wideband system modulation frequencies up to 20% of the carrier frequency may be accommodated (IRIG<sup>16</sup>, page 37). For the greatly extended bandwidth FM system referred to in the previous paragraph a higher modulation index is used.

In the wideband system (deviation  $\pm 40\%$  of the carrier frequency) of FM recording, the system most widely used, accuracies of about 2% can be readily achieved.

The following is a summary of the advantages as applied to the wideband system of FM recording:

- (i) Recording of data down to DC is possible.

- (ii) Amplitude instability caused by tape drop-outs does not significantly degrade the overall accuracy.

- (iii) Data signals can be readily reproduced with high signal to noise ratios (greater than 40 db).

- (iv) Moderately large data bandwidths can be accommodated. It is relatively easy to obtain a flat frequency response over the specified bandwidth.

- (v) The non-linear phase characteristic of the tape recorder does not give rise to phase distortion.

- (vi) Data can be readily recorded and reproduced with good accuracy (2%).

- (vii) Crosstalk between adjacent channels is relatively low.

The chief disadvantage of FM recording is that tape speed variations between record and replay show up as noise on the demodulated data. Hence high demands are placed on the tape speed stability of record and replay machines.

#### A1.4. Pulse Duration Modulation

In the pulse duration modulation (PDM) system of recording the data is sampled at discrete intervals and the duration of a pulse is made proportional to the level of the data signal at the

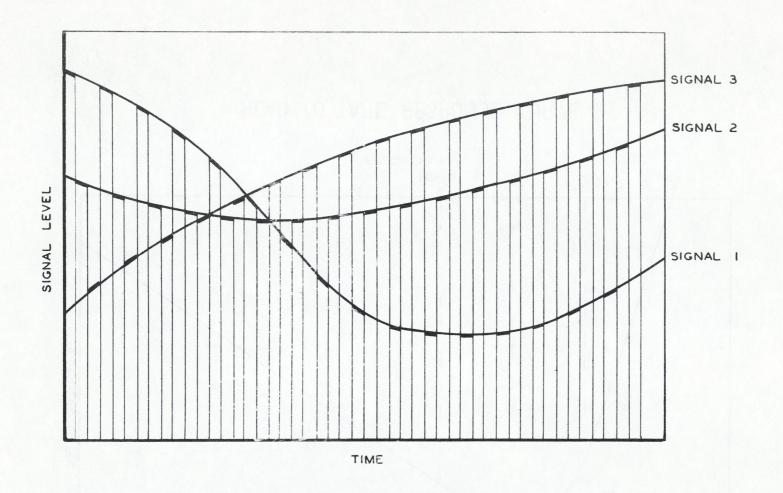

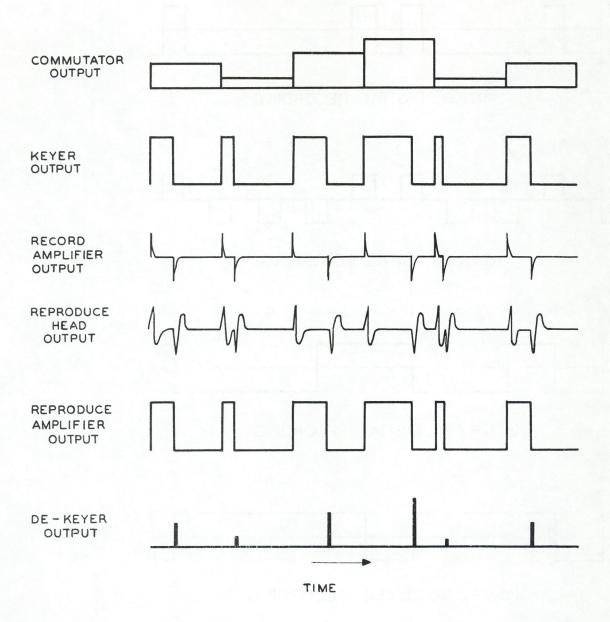

time of sampling. For discussion on the PDM record system refer to Weber,<sup>3</sup> IRIG,<sup>16</sup> Axon,<sup>23</sup> Borwick<sup>24</sup> and Halfhill.<sup>25</sup> Normally a number of data channels are multiplexed on a time division basis in this system of recording. Time division multiplexing of three data signals is illustrated in Fig. 2. The unit which converts a voltage level to a proportional pulse duration is called a "keyer." The PDM waveform appearing at the output of the keyer is differentiated by the record amplifier so that only the leading and the trailing edges of the pulses are recorded on the tape. On replay a normal PDM waveform is reconstructed by means of the reproduce amplifier. The PDM waveform is converted to a pulse height waveform by a de-keying unit. Individual channels are separated by means of a de-multiplexer. For any given channel the output from the de-multiplexer is discontinuous. By passing the output through a suitable filter a smooth waveform virtually identical to the recorded data waveform results.

The standard keying rate of 900 per second has been set by the Inter-Range Instrumentation Group for telemetry and tape recording. Any combination of number of sampled parameters and channel sampling rate may be employed provided 900 per second keying rate is maintained (e.g.  $90 \times 10$ ,  $45 \times 20$ ,  $30 \times 30$ , etc.). Normally one or two channels of the multiplexer are used for frame synchronization and two for zero and full scale calibration signals. Frame synchronization pulses must be recorded to enable the ground station data reduction equipment to identify channels.

At least six samples per cycle of a sinewave are required in order to enable accurate reconstruction to be made. The upper frequency limit of the data to be recorded will therefore be approximately one-sixth of the sampling rate for a particular channel. For channels which are sampled once per scan of the multiplexer the following table applies:

| Multiplexer           |                                          | Signal Information  |                                   |  |

|-----------------------|------------------------------------------|---------------------|-----------------------------------|--|

| Number of<br>Channels | Speed in<br>Complete Scans<br>per Second | Number of Channels* | Upper<br>Frequency<br>Limit-Hertz |  |

| 90                    | 10                                       | 86                  | 1.7                               |  |

| 45                    | 20                                       | 41                  | 3.3                               |  |

| 30                    | 30                                       | 26                  | 5                                 |  |

| 20                    | 45                                       | 16                  | 7.5                               |  |

| 10                    | 90                                       | 6                   | 15                                |  |

| 1                     | 900                                      | 1†                  | 150                               |  |

<sup>\*</sup> Allowing two multiplexer channels for synchronization purposes and two for calibration (except †).

To obtain a better frequency response for a particular information channel it is possible to utilize more than one multiplexer channel and hence achieve a higher effective sampling rate for that information channel.

The pulse durations normally used are tabulated below:

| Input Signal Voltage | Pulse Duration  |

|----------------------|-----------------|

| 0                    | 90 microsecond  |

| 5 volts (Full Scale) | 660 microsecond |

The total interval available between samples is 1100 microsecond approximately and the dynamic range according to the above table is 570 microsecond.

<sup>†</sup> No synchronizing pulses required, also no calibration signals have been included.

The precision with which the pulse duration may be recorded will be dependent on the tape speed employed and hence the overall accuracy will be degraded at the lower tape speeds assuming that the standard 900 per second sampling rate is invariant. Weber<sup>3</sup> states that the PDM process is capable of recording an effective 40 sinewave cycles per inch of tape. Assuming that six samples are required per cycle then the 40 sinewave cycles per inch of tape would be equivalent to 240 samples per inch. The latter figure corresponds to the normal keying rate (900 per second) at a tape speed of  $3\frac{3}{4}$  inches per second ( $900/3\frac{3}{4} = 240$ ). Systems conforming to IRIG specifications (IRIG<sup>16</sup> Sec. 6.4.5) are required to have the characteristics tabulated below:

| Tape Speed inch per second | Minimum Pulse Duration microsecond | Accuracy<br>microsecond |

|----------------------------|------------------------------------|-------------------------|

| 60                         | 75                                 | ±2                      |

| 30                         | 75                                 | $\pm 2$                 |

| 15                         | 100                                | $\pm 3$                 |

Assuming a dynamic range of 570 microsecond an accuracy of approximately  $\pm 2/570$  (0·35%) should be attainable at 30 ips and 60 ips and an accuracy of  $\pm 3/370$  (0·53%) should be attainable at 15 ips. Generally an accuracy of better than 1% is attributed to the PDM system but as outlined above this will be dependent on tape speed. Referring to the above table it is to be noted that the minimum pulse duration which may be used increases as tape speed is reduced. Even at 15 ips the IRIG specification gives a figure of 100 microsecond for minimum pulse duration which is slightly greater than the 90 microsecond typically used as the zero input equivalent pulse duration. The limitation of minimum pulse duration arises because sufficient time has to be allowed for the leading edge replay pulse to decay (Fig. 3) before the trailing edge pulse appears. Hence minimum pulse duration will represent a major limitation at the lower tape speeds.

Tape flutter and wow present less problems in the PDM system than in the FM system. Only the integrated flutter and wow timing error over the pulse duration time is of significance.

Generally the PDM system is very useful for recording, at better than 1% accuracy, a multiplicity of data signals having relatively low frequency content.

#### A1.5. Pulse Code Modulation

In the pulse code modulation (abbreviated as PCM and also referred to as "digital") system of recording, the data is converted to a code consisting of a series or group of binary digits which are recorded on tape (Weber,³ Halfhill,² Godinez,² and Leach Corp.² 7). The heart of the pulse code modulator is the analogue to digital converter (frequently abbreviated as ADC) which converts the analogue outputs from the transducers into a digital form. Normally a sampling technique, similar to that for PDM, is used to enable time multiplexing of a number of channels. For the high sampling rates normally used a solid state multiplexer is the obvious choice. Accuracy in the digital system, with the exception of occasional erroneous output data due to tape dropouts, is not dependent on the tape record/replay system (unlike all the forms of analogue recording) but depends only on the characteristics of the ADC and the multiplexer. The possible accuracy of the digital recording system depends on the resolution of the ADC as indicated in the following table:

| Number of Binary Digits | Possible Accuracy                        |

|-------------------------|------------------------------------------|

| 5                       | 1 part in 2 <sup>5</sup> (or 32) 3%      |

| 7                       | 1 part in 27 (or 128) 1%                 |

| 10                      | 1 part in 2 <sup>10</sup> (or 1024) 0·1% |

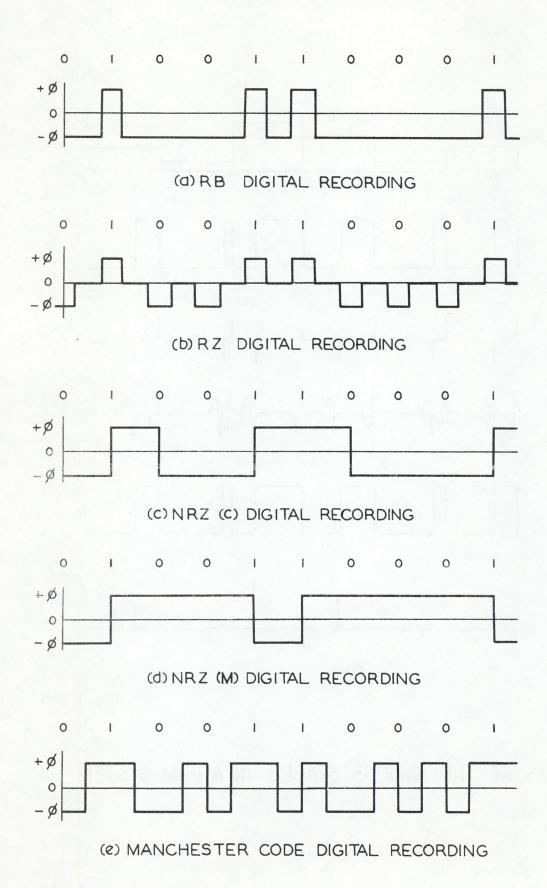

Data may be recorded in serial form on one or more tracks or may be recorded in parallel on multiple tracks. Digital recording is accomplished by magnetizing the tape to saturation in both directions in one of the following ways (Weber<sup>3</sup> and Godinez<sup>26</sup>):

#### (i) Return to Bias (RB)

The tape is magnetically biased to a predetermined level in one direction (say —) and the "ones" are recorded by magnetizing the tape in the opposite polarity (Fig. 4(a)). After each pulse for a "one" the tape returns to the bias condition.

#### (ii) Return to Zero (RZ)

The tape is normally in a demagnetized state and "ones" and "zeros" are assigned opposite polarities. A pulse is recorded for each digit (Fig. 4(b)).

#### (iii) Non Return to Zero—Change NRZ(C)

The tape is always saturated in one direction or the other, the reversals in polarity occurring each time a change in bits occurs (Fig. 4(c)).

#### (iv) Non Return to Zero—Mark NRZ(M)

Polarity is reversed each time a "one" is recorded (Fig. 4(d)).

#### (v) Manchester Code (also referred to as Ferranti Code or Phase Modulation)

The clock is mixed with the data before recording (Fig. 4(e)). By eliminating the long intervals when no transition occurs (as may occur in NRZ) a higher degree of immunity against tape dropouts results.

Godinez<sup>26</sup> compares the various recording techniques for rugged environment conditions. He provides the following comparison table.

| Recording<br>Technique | Maximum<br>Packing<br>Density                  | Dropout<br>Accuracy                                               | Comments                                                                                                                                     |

|------------------------|------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| RB                     | 600 bit/inch                                   | 1 × 10 <sup>5</sup>                                               | (1) Inefficient bandwidth utilization (2) Poorest of record systems                                                                          |

| RZ                     | 300 bit/inch                                   | 1 × 10 <sup>6</sup>                                               | (1) Lowest bandwidth utilization                                                                                                             |

| NRZ(C)                 | 600 bit/inch<br>1000 bit/inch<br>2000 bit/inch | $1 \times 10^{6}$ $1 \times 10^{5}$ $1 \times 10^{4}$             | <ol> <li>(1) IRIG standard for recording</li> <li>(2) Simple electronics</li> <li>(3) Accuracy dependent on packing density</li> </ol>       |

| NRZ(M)                 | 600 bit/inch<br>1000 bit/inch<br>2000 bit/inch | $0.5 \times 10^{6}$<br>$0.5 \times 10^{5}$<br>$0.5 \times 10^{4}$ | (1) Often used recording method (2) Slightly better than NRZ(C) in accuracy                                                                  |

| Manchester<br>Code     | 1000 bit/inch<br>800 bit/inch                  | $1 \times 10^{7} \\ 1 \times 10^{8}$                              | <ul><li>(1) Most accurate recording scheme</li><li>(2) More complex electronics</li><li>(3) Density limited to under 1000 bit/inch</li></ul> |

The PCM system places stringent demands on tape uniformity and head to tape contact (Weber³) to minimize tape dropouts (Franck³). The latter condition requires an extremely fine finish on the surface of the head, adequate tape pressure and a minimum tendency of the head to collect oxide particles from the surface of the tape. Some degree of immunity from tape dropouts is achieved by means of redundant check (or parity) characters. Another aspect which requires careful attention if characters are recorded in parallel is that of tape skew which arises if the centre line of the tape departs from a perpendicular to the line of record and reproduce head gaps. The problem becomes a major one at high packing densities as corresponding bits on different tracks tend to become misaligned.

The PCM system of recording is relatively insensitive to wow and flutter in the tape transport. It provides the greatest accuracy of all the recording systems. To achieve the high overall accuracy the transducers, multiplexer and ADC must each have high precision.

#### A1.6. Comparison of Recording Techniques

A comparison of the various recording systems is made in the following table (overleaf).

#### COMPARISONS OF RECORDING PROCESSES

| Characteristic                      | Direct                                                     | Carrier Erase                                            | FM<br>(Standard Wideband)                               | PDM                                                                   | PCM                                                                           |

|-------------------------------------|------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Low frequency limit                 | 50 Hz at $7\frac{1}{2}$ ips<br>300 Hz at 60 ips            | 0 Hz                                                     | 0 Hz                                                    | 0 Hz                                                                  | 0 Hz                                                                          |

| High frequency limit                | 250 KHz at 60 ips<br>125 KHz at 30 ips<br>60 KHz at 15 ips | 10 KHz at 60 ips<br>5 KHz at 30 ips<br>2·5 KHz at 15 ips | 20 KHz at 60 ips<br>10 KHz at 30 ips<br>5 KHz at 15 ips | Approx. $150/n$ at $3\frac{3}{4}$ ips where $n$ is number of channels | Up to approx. $80/n$ Hz at 30 ips for system proposed $(n = No. of channels)$ |

| Figure of merit (cycles per inch)   | 4160                                                       | 166                                                      | 333                                                     | 40                                                                    | 3                                                                             |

| Effect of 1% change in tape speed   | 1% change in frequency.<br>Small change in<br>amplitude    | 1% change in frequency.<br>Small change in<br>amplitude  | 2·5% error signal                                       | 1% magnitude error                                                    | None                                                                          |

| Dynamic range                       | 25 db typical                                              | 20 db typical                                            | 46 db typical                                           | 52 db typical                                                         | No noise introduced in the recording process                                  |

| Channels per track                  | Usually one, several with frequency multiplexing           | Usually one                                              | Usually One                                             | Up to 86 channels time multiplexed                                    | Any number may be time multiplexed                                            |

| Accuracy                            | 5–10%                                                      | 5–10%                                                    | 2%                                                      | 1%                                                                    | 0·1% Typical                                                                  |

| Linearity                           | 5%                                                         | 5%                                                       | 1%                                                      | 0·5% Typical                                                          | Depends on ADC.<br>Best linearity of all systems                              |

| Effect of tape dropouts             | Produces large amplitude changes                           | Produces large amplitude changes                         | Very little effect                                      | Normally no effect                                                    | May give erroneous<br>readings. This system<br>requires minimum dropouts      |

| Crosstalk between adjacent channels | Quite high at low<br>frequencies and high tape<br>speeds   | Low                                                      | Very low                                                | Nil                                                                   | Nil                                                                           |

| Circuit complexity                  | Simple                                                     | Simple                                                   | Moderate                                                | Complex                                                               | Complex                                                                       |

#### A2. TECHNIQUES SUITABLE FOR USE IN AIRBORNE DATA RECOORDING

Some of the measurements likely to be required in aircraft performance studies are summarized below and the appropriate recording techniques are indicated.

(i) Frequency Range 50 Hz to 250 KHz, Accuracy 10%

Voice which is normally recorded in conjunction with data falls in this category as very low frequency response is not required and 10% accuracy is quite adequate.

Occasional input signals with very high upper frequency limit (up to 50 KHz) arising in the measurement of vibrations and noise on jet engines need to be recorded.

Direct recording techniques are normally used for voice recording and must be used for the high frequency vibration recording.

(ii) Frequency Range 0 to 20 KHz, Accuracy 2%

Most vibration measurements fall into this category. Vibration frequencies as low as 2 Hz are quite common. Usually an accuracy of 2% is adequate for vibration measurement, whereas the 10% accuracy offered by the direct recording system is generally unacceptable.

Pressure measurements ranging from static to dynamic with high frequency content also fall in this category.

Noise measurements requiring better accuracy and better low frequency performance than that obtainable using direct recording techniques also fall into this category.

Other quantities requiring measurement down to DC are temperature, force, strain and the like.

Wideband FM techniques (1 channel per track) are normally used for the recording of these quantities.

(iii) Frequency Range 0 to 150 Hz (based on 1 information channel, proportionately lower for a greater number of channels), Accuracy 1%.

There are a large number of measurements to be made on aircraft which involve signals that can be regarded as static or quasi-static. Some of these are:

- (a) Pressures

- (b) Temperatures

- (c) Control surface angles

- (d) Strains, forces and loads (picked up from strain gages)

- (e) Aircraft pitch, roll and yaw (picked up from gyros)

- (f) Aircraft heading (picked up from compass)

A large number of these quantities may require measurement during any given test and time division multiplexing is desired. PDM techniques can be readily used for these measurements.

It is to be noted that the standard keying rate of 900 per second for the PDM system as specified by IRIG<sup>16</sup> limits the upper frequency limit to approximately 150 Hz for one information channel. However, this response is feasible at  $3\frac{3}{4}$  ips tape speed. Higher keying rates at higher tape speeds would allow increased data signal bandwidths to be obtained.

Many measurements which can be recorded using PDM techniques can also be recorded more accurately using PCM techniques. However, the PDM system offers higher information packing density on the tape than the PCM system (40 cycle per inch as compared with 3 cycle per inch). If the IRIG standard keying rate is used then the frequency response obtainable at  $3\frac{3}{4}$  ips for the PDM system would be approximately the same as that obtainable at 60 ips for the PCM system referred to below.

(iv) Frequency Range 0 to 150 Hz (based on one information channel, proportionately lower than for a greater number of channels), Accuracy 0.1%.

A small number of flight parameters including airspeed, altitude, air temperature, jet pipe temperature, engine speed and fuel flow often require measurement to high accuracy. High precision is required because basic computed quantities such as true airspeed, Mach number, rate of climb, overall drag and net thrust are functions of several of these parameters, and if the final answers are to be sufficiently accurate, and especially if one is looking for small improvements or changes in performance, then no lower precision is acceptable. PCM (digital) recording is the only feasible method of achieving the required accuracy.

The bandwidth of approximately 150 Hz is that obtainable for one channel of serial digital data recorded at 60 ips tape speed. Proportionately lower bandwidths would be obtained at lower tape speeds.

## A3. SIGNAL CONDITIONING REQUIREMENTS RELEVANT TO AIRBORNE DATA RECORDING

#### A3.1. Transducers and Associated Signal Conditioning Equipment

The function of the signal conditioning equipment is to accept the "raw" input data signals, usually derived from suitable transducers, and provide outputs acceptable to the tape recorder. Such functions as amplification, attenuation, zero shifting, impedance changing and filtering are required of the signal conditioning equipment. So that tape recorder plug-ins may be interchanged in the field without the need for re-alignment it is desirable that 100% input level to the tape recorders be rationalized to a standard level (1 volt R.M.S. seems to be a generally adopted standard). Hence it is the function of the signal conditioning equipment to provide outputs for the tape recorders based on the standard 100% level.

The tape recorder inputs are usually single ended (one side is connected to case which is in turn connected to the recorder supply common). Normally the outputs of the signal conditioning equipment are connected to the tape recorder input via co-axial cable. The co-axial cable connection provides good immunity from pick-up but in situations where the signal conditioning equipment is placed remotely from the tape recorder the shunt capacitance may be quite significant. So that satisfactory operation may be obtained in such cases it is essential that the output of the signal conditioning equipment be unaffected by moderate capacitance loading (50 feet of co-axial cable at 30 pF per foot giving a total of 1500 pF should be accommodated).

The minimum impedance as seen at the recorder inputs is typically 10 kilohm and hence the output impedance of the signal conditioning equipment should be low in comparison. Another reason why the output impedance of the signal conditioning equipment should be kept low is to prevent high frequency roll-off because of the capacitance loading. To meet these requirements the output impedance of the signal conditioning equipment should normally be kept below about 100 ohm.

A wide variety of transducers is required for use in the measurement of physical quantities such as pressure, temperature, displacement, velocity and acceleration. Invariably the transducers provide an electrical output. Normally the output is a direct analogue of the physical quantity being measured but transducers having digital output have also become available in recent years. Transducers may be broadly classified according to their principle of operation. Some of the more common types of transducer will now be briefly considered with a view to indicating the signal conditioning requirements.

#### (i) Potentiometer Type

In this type of transducer a change in the physical quantity being measured causes the wiper of a precision potentiometer to be displaced. A typical application is in the measurement of relatively large linear or angular displacements.

The potentiometer type transducer requires a stable DC or AC supply. Usually the full scale output of these devices is sufficient to allow direct connection to the tape recorder input.

#### (ii) Strain Gage Type

The strain gage transducer is used for the measurement of a large number of physical parameters such as displacement, acceleration, force, pressure and the like. The most commonly used strain gage transducer has an unbonded wire filament strain gage which forms the active arm of a Wheatstone Bridge circuit. The strain gage bridge is supplied with stable DC or AC, typically about 5 volt, and the bridge output is typically about 5 millivolt full scale.

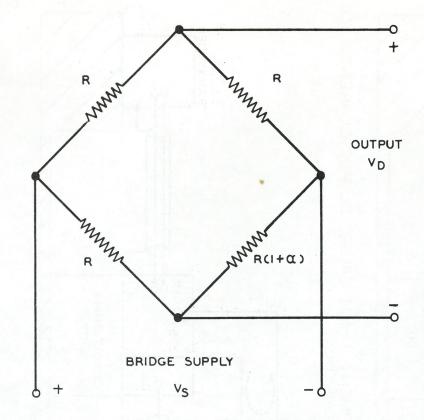

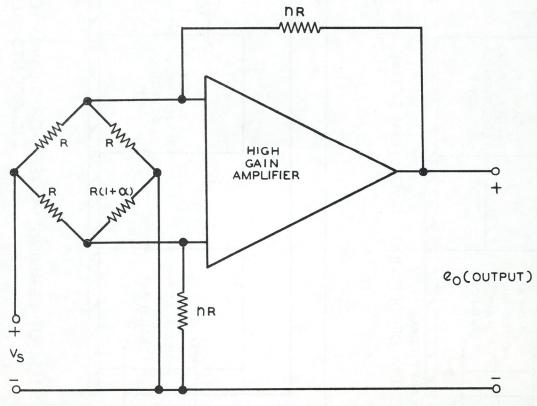

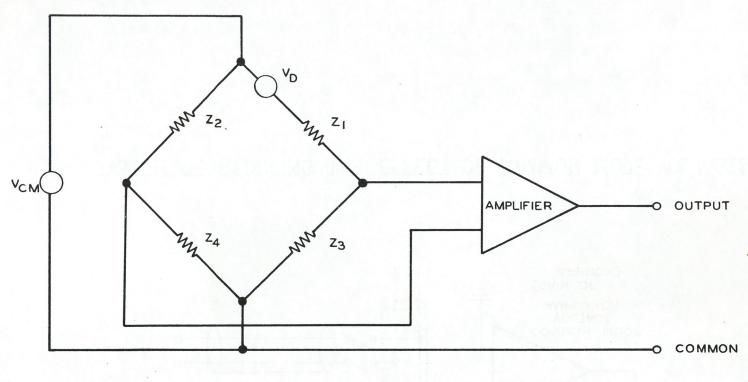

The outputs from wire strain gage transducers require amplification before being taken to the tape recorder inputs. In Fig. 5(a) a typical strain gage bridge has been drawn. An amplifier having a single ended input may be used if a completely isolated supply is used for the bridge. However, such an arrangement does not permit more than one strain gage transducer to be operated from any given bridge supply. A better solution is to use an amplifier having a differential input. Under these conditions one side of the bridge supply may be connected to the amplifier common and hence a number of transducers may be operated from the one supply. In addition a differential input amplifier has much lower drift than an amplifier with single ended input if a chopper is not used. Drift is a very important consideration when the transducer is excited from DC and response down to DC is required. In Fig. 5(b) a method of connecting the bridge circuit to a high gain amplifier with differential input is illustrated.

If the bridge, which is considered to be initially balanced, is unbalanced by  $\alpha R$  in one arm, then, referring to Fig. 5(a), the open circuit output voltage  $V_D$  is given by

$$\begin{split} \boldsymbol{V}_{D} &= \left(\frac{1+\alpha}{2+\alpha} - \frac{1}{2}\right) \boldsymbol{V}_{S} \\ &= \frac{\alpha}{4(1+\alpha/2)} \, \boldsymbol{V}_{S} \\ &\simeq \frac{\alpha}{4} \, \boldsymbol{V}_{S} \qquad \qquad \text{for } \alpha \ll 1 \text{ which is usually a good approximation.} \end{split}$$

If the bridge having this same unbalance is connected to the amplifier as indicated in Fig. 5(b) then the output voltage will be given approximately by

$$e_0 = 2nV_D$$

$$= \frac{\alpha nV_S}{2} \qquad \text{assuming } \alpha \ll 1 \text{ and } n \gg 1.$$

The amplifier must have high common mode rejection and for strain gages supplied with DC it is essential that the amplifier drift be very low.

Semiconductor strain gages having much higher outputs than the conventional wire gage are also available. The linearity of the semiconductor type is, however, not as good as the wire type.

#### (iii) Capacitance Type

In capacitance type transducers the capacitance of the sensing element varies with the measurand. In order to obtain an electrical output it is necessary to supply an external voltage to the transducer. One method for obtaining the requisite output is to use an AC bridge. Another method uses the transducer capacitance change to vary the frequency of an oscillator. Such quantities as displacement (proximity type transducer), pressure, temperature and the like may be measured with this type of transducer. Response down to DC is possible.

#### (iv) Piezo Electric Type

In this type of transducer which utilizes the piezo-electric effect the charge on a crystal (which appears electrically as a capacitor) varies with the measurand. The transducer is a self-generating type and therefore requires no external voltage supply. It is used frequently for the measurement of acceleration, pressure, sound level and the like. Since piezo-electric transducers generate charge proportional to the measurand, the voltage as seen at the transducer terminals will depend on the capacitance loading. Response down to DC is not possible, the lower cut-off frequency being determined by the value of the effective shunt capacitance and resistance components as seen at the transducer terminals. Frequently high input impedance voltage amplifiers are used in conjunction with these transducers to provide the necessary amplification and impedance change. In such instances transducer re-calibration is necessary whenever the capacitance loading on the transducer is changed such as occurs if a different connecting cable is used.

Charge amplifiers (amplifiers which provide an output voltage proportional to input charge) provide the best form of signal conditioning equipment for use with piezo-electric transducers as transducer calibration is unaffected by changes in the shunt capacitance across the transducer. Very low cut-off frequencies of the order of a small fraction of 1 Hz are fairly easily achieved when charge amplifiers are used.

#### (v) Inductance Type

Three main types of inductive transducer, the velocity type, the variable reluctance type and the linear variable differential transformer (L.V.D.T.) type will be considered.

The velocity type transducer is self generating. Motion of a magnet within a coil generates an output voltage proportional to the velocity of the magnet relative to the coil. Such transducers are used for measuring velocity and are frequently used in vibration work. Sensitivities covering a broad range are available and are typically some hundreds of millivolts full scale for vibration transducers. Some amplification is usually required to bring the signals to a level suitable for most tape recorders. Typically an AC amplifier with a gain of up to 20 and an input impedance of approximately 10,000 ohm would satisfy most requirements.

In the variable reluctance type of transducer a slug of magnetic material moves between two coils. Changing the slug position changes the reluctance of the coils which in turn changes the impedance of an electrical circuit in which the coils are connected. Such transducers require AC excitation. Frequently the variable reluctance type transducer is used for measuring displacement and pressure. These transducers are usually small, have fast response time and show good immunity from shock and vibration. Response down to DC is possible. The signal conditioning equipment required consists of an oscillator (of frequency at least 10 times that of the maximum frequency of interest of the measurand) and an amplifier having a phase sensitive demodulator. Usually the output is relatively high and little amplification is required.

In the L.V.D.T. type of transducer the sensing element moves an armature inside the three coils of a differential transformer. One of the coils (called the primary coil) is energized with AC. The coupling from the primary coil to each of the other two coils (called the secondary coils) is changed equally but in opposite senses due to a displacement of the armature. The L.V.D.T. requires AC excitation of a specific frequency which is usually relatively low (50 Hz, 60 Hz, and 400 Hz are typical). Any given L.V.D.T. requires to be matched to the associated signal conditioning equipment. Response down to DC is possible. A phase sensitive demodulator is required to give an output voltage which is the analogue of the measurand. The output of the L.V.D.T. is usually quite high, the shock and vibration immunity poor, and the frequency response low (less than 40 Hz). The L.V.D.T. type of transducer is used mainly for the measurement of displacement and pressure.

#### (vi) Thermocouple Type

The thermocouple type transducer employs the Seebeck effect (i.e. an e.m.f., produced in a circuit containing two conductors having two junctions at different temperatures, varies with temperature difference between the junctions). This type of transducer is frequently used for the measurement of temperature. Usually the thermocouple itself contains only one junction (often referred to as the "hot" junction). In order to measure temperature a "cold" junction which is held at a fixed temperature (usually 0 °C) or a circuit simulating an isothermal junction is required. For a chromel-alumel thermocouple the output is approximately 4 millivolt per 100 °C temperature difference.

A DC amplifier having typically a gain of about 100 and a cold junction compensating circuit are required. The latter may readily be realized with the aid of a bridge circuit containing a temperature sensitive resistance.

In order to make measurements to the accuracy required of the digital recording system very accurate and repeatable transducers are required. These are not readily available and hence very careful selection is required. Similarly the accuracy of the signal conditioning equipment has to be very high for the digital system.

There are a number of relatively small self-contained amplifiers commercially available for use as signal conditioners in an airborne environment. These amplifiers are normally mounted separately in close proximity to their associated transducers. In the accompanying table the main characteristics of some typical amplifiers have been tabulated. Amplifiers Nos. 1 and 2 may be used for general purpose amplification of AC voltage signals such as would be obtained from velocity type transducers. Amplifiers Nos. 3 and 4 are charge amplifiers and hence would be used in conjunction with piezo-electric transducers. Amplifier No. 5 is suitable for use with strain gages and could also be used in conjunction with thermocouple transducers.

It is sometimes more convenient, particularly where a large number of transducers is involved to locate all the signal conditioning amplifiers in a single cabinet. To allow amplifiers to be readily interchanged when transducers are changed a plug-in type construction is preferred. (Self contained amplifiers of the type referred to in the previous paragraph cannot be conveniently interchanged if mounted in a single cabinet.) The power supply requirements for a range of amplifiers can usually be rationalized to just a few regulated supply rails using the single cabinet construction. To the author's knowledge a suitable range of plug-in type airborne signal conditioning amplifiers is not available commercially. A summary of some of the plug-in amplifiers required as signal conditioners follows on p. 17.

### CHARACTERISTICS OF SOME TYPICAL SIGNAL CONDITIONING AMPLIFIERS

| Reference No.             | 1                                                                                                                      | 2                                                            | 3                                                              | 4                                                                                                                          | 5                                                                                                                                                  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Type                      | Columbia Model 5203<br>AC Voltage Amplifier                                                                            | Ad-Yu Model A102E<br>AC Voltage Amplifier                    | Gulton Model FT-3512<br>Charge Amplifier                       | Endevco Model 2640<br>Charge Amplifier                                                                                     | CEC Type 1-362-001<br>DC Amplifier                                                                                                                 |

| Input Arrangement         | Single Ended                                                                                                           | Single Ended                                                 | Single Ended                                                   | Single Ended                                                                                                               | Differential                                                                                                                                       |

| Output Arrangement        | Single Ended                                                                                                           | Single Ended                                                 | Single Ended                                                   | Single Ended                                                                                                               | Single Ended                                                                                                                                       |

| Input Impedance           | > 200M shunted by not<br>more than 20pF                                                                                | 100K                                                         |                                                                |                                                                                                                            | > 1M                                                                                                                                               |

| Gain                      | Adjustable from 2 to 50                                                                                                | Fixed, 100 or 10 (selectable via a switch)                   | Adjustable, 2mV/pcmb to 40mV/pcmb                              | Adjustable, 2mV/pcmb to 20mV/pcmb                                                                                          | 125 nominal, adjustable $\pm 10\%$                                                                                                                 |

| Frequency Response        | Flat within ±5%<br>2 Hz to 50 KHz                                                                                      | Flat within ±3db<br>1 Hz to 5 MHz                            | Flat within ±2%<br>5 Hz to 10 KHz                              | Flat within ±5%<br>3 Hz to 20 KHz                                                                                          | Flat within 0·1db<br>DC to 2 KHz                                                                                                                   |

| Maximum Output Voltage    | 5 V peak to peak                                                                                                       | 11·2 V peak to peak                                          | 5·2 V peak to peak                                             | 2.8 V peak to peak                                                                                                         | 10 V peak to peak into<br>10K                                                                                                                      |

| Maximum Output Current    | 0.5 mA peak to peak                                                                                                    | 0.8 mA peak to peak                                          |                                                                |                                                                                                                            | ±0.5 mA                                                                                                                                            |

| Output Impedance          | 100 ohm max.                                                                                                           | 100 ohm max.                                                 |                                                                | 50 ohm                                                                                                                     | 250 ohm max.                                                                                                                                       |

| Noise Level               | 4 mV peak to peak<br>referred to the input<br>with the gain set at 50<br>and the input shunted by<br>600 pF or greater | 6 μV equivalent input<br>noise with input short<br>circuited | 20 mV peak to peak at<br>the output at a gain of<br>40 mV/pcmb | 0.019 pcmb. R.M.S. per<br>100 pF source capaci-<br>tance (referred to input)<br>or 1.5 mV R.M.S. which-<br>ever is greater | Less than 10 mV peak to peak measured at the output with the input short circuited over the band 0·1 Hz to 5 KHz                                   |

| Total Harmonic Distortion |                                                                                                                        |                                                              |                                                                | 1% max.                                                                                                                    |                                                                                                                                                    |

| Common Mode Rejection     |                                                                                                                        |                                                              |                                                                |                                                                                                                            | Greater than 100db                                                                                                                                 |

| Output Zero               |                                                                                                                        |                                                              |                                                                |                                                                                                                            | Drift less than ±10µV referred to input in 8 hrs. at 77°F. Shifts 0.005% of Full Scale per deg. F from 0°F to 200°F. Adjustable ±5% of Full Scale. |

| Other Outputs             |                                                                                                                        |                                                              |                                                                |                                                                                                                            | Bridge excitation supply 10 V. This supply is completely isolated.                                                                                 |

| Power                     | 28 $\pm$ 3 V DC at 25 mA                                                                                               | 19.6 V at 3 mA<br>Internal battery                           | 28 V DC at 27 mA                                               | 28 + 4 V DC at 20 mA<br>- 8                                                                                                | 28 ± 4 V DC at 100 mA                                                                                                                              |

- (i) AC amplifiers having single-ended input and variable gain up to approximately 200 for transducers with single-ended output.

- (ii) Differential input low drift DC amplifiers for use with strain gages and thermocouples.

- (iii) Charge amplifiers for use with piezo-electric transducers.

- (iv) Differential input AC amplifiers with phase sensitive demodulators for use with variable reluctance transducers, L.V.D.T.'s and AC excited strain gages.

In addition to amplifiers other equipment such as filters, and in the case of AC excited transducers, precision oscillators are required.

Development of suitable plug-in amplifiers is at present being undertaken at these laboratories.

#### A3.2. Power Supplies for Signal Conditioning Equipment

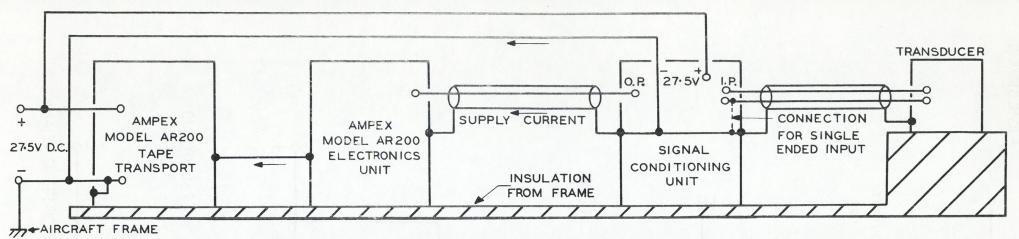

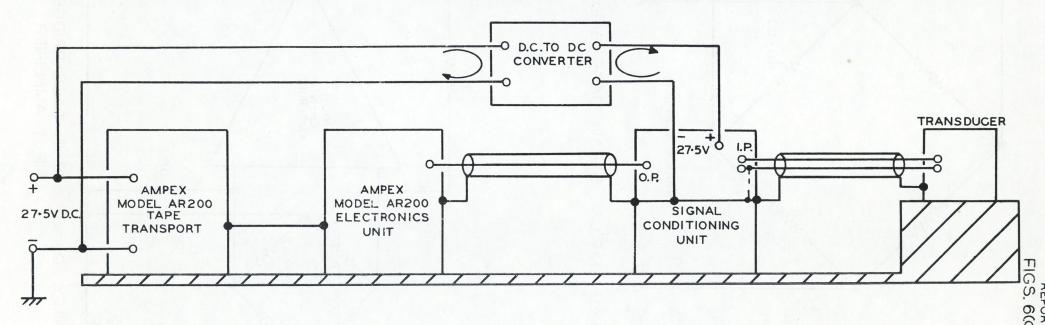

In order to amplify low level transducer signals with a minimum of noise and interference considerable care has to be exercised in the selection or design of power sources. It is essential that "earth" currents such as those arising in an aircraft frame do not flow via signal common lines. Currents flowing through the frame of the aircraft are considerable and millivolt drops across the earthing system are quite possible. The single point earthing technique is usually used to prevent voltage drops in the earthing structure from being picked up with the signals.

As a typical example the Ampex Model AR200 airborne analogue tape recorder derives power from the normal aircraft 27·5 V.D.C. supply, the negative side of which is connected to the aircraft frame. Further the Ampex Model AR200 accepts single-ended input signals the common side of which is connected to the recorder case and also to the supply negative. In Fig. 6(a) a block diagram of a typical recording system using this recorder is shown. The signal conditioning equipment derives power from the aircraft supply in such a way as to cause supply currents to flow through the signal common shields between the signal conditioning unit and the electronics unit. Such an arrangement is poor practice and may be obviated if a DC to DC converter is added as illustrated in Fig. 6(b). Apart from the improved earthing arrangement resulting from the latter technique there is the advantage that a number of supply rails either positive or negative, completely isolated from each other if need be, may be readily furnished. For DC amplifiers providing zero volts output under zero signal conditions both positive and negative supply rails are necessary.

The advantages which arise when a DC to DC converter is used may equally be achieved by the use of self-contained batteries. However, batteries are usually bulky and require frequent attention either in relation to charging or replacement. In addition the temperature range over which batteries can be operated is frequently inadequate.

Similarly the appropriate DC supplies may be obtained from the aircraft 115V 400 Hz supply with the aid of a transformer and associated circuits. While such an arrangement is quite feasible in most aircraft, it presents problems if data has to be acquired elsewhere such as on board ships or in the field.

Regulated supplies of various voltages are required throughout the signal conditioning equipment as power sources for amplifiers, strain gages and the like. In the case of the plug-in signal conditioning amplifiers at present under development at these laboratories the selection of supply rail voltages is usually dictated by the requirements of the linear integrated circuits used. Most linear integrated circuits can be accommodated by voltage rails  $\pm 5V$ ,  $\pm 10V$  and  $\pm 15V$ . This selection of supply rails is also consistent with the 10V supply usually required for strain gage bridges and by the 5V supply required by many digital integrated circuits.

#### PART B REQUIREMENTS FOR A HYBRID RECORDING SYSTEM

#### **B1. ANALOGUE RECORD SYSTEM EXTENSIONS**

Most manufacturers of instrumentation magnetic tape recorders provide complete recording and replaying facilities for use with the direct recording system. Adjustments are usually provided on the record amplifiers for bias level and amplifier sensitivity, and on the reproduce amplifiers for the shape of the overall record/replay frequency response. The adjustments

required for shaping the frequency response are invariably difficult and time consuming, particularly as the record and replay head characteristics have to be taken into account.

A system of recording speech and a reference frequency on a single direct recording channel has been developed at these laboratories and is described in Sec. B1.1.

Many manufacturers provide complete recording and replaying facilities for use with the wideband (maximum deviation  $\pm 40\%$  of carrier frequency) FM system. Adjustments are provided to allow alignment of record and reproduce amplifiers. FM record and reproduce amplifier alignment is usually a very simple procedure. As the record and replay head characteristics have virtually no effect on alignment the record and reproduce amplifiers can be independently aligned. An FM calibration unit, such as the Ampex Model TC-10, may be used to facilitate amplifier alignment.

Improved signal to noise ratios are possible with the FM system of recording by using servo speed control of the tape reproducer machine and by using flutter compensation techniques. Some development along these lines has proceeded at these laboratories and is discussed in Sec. B1.2.

The PDM recording system usually requires fairly complex data acquisition and reduction equipment which are not normally supplied by tape recorder manufacturers. Ampex Corporation, for instance, provides a PDM record amplifier which accepts information already in PDM form and provides suitable record head output. No multiplexing or keying equipment is provided by the above manufacturer. Similarly no de-keying or de-multiplexing equipment is provided on the reproduce side. Some manufacturers of data acquisition and reduction equipment produce keying and de-keying equipment for use with the PDM system. However, PDM systems frequently require to be adapted to the particular needs of the user, a factor which makes standardization of equipment difficult.

In Sec. B1.3 the PDM system requirements are analysed and lines of future expansion are indicated. In particular the use of digital computer techniques for reduction purposes is considered.

#### **B1.1.** Recording of Reference Frequencies

The recording of appropriate reference frequencies is required for the following reasons:

- (i) To check the speed stability of the recorder tape transport.

- (ii) To enable servo speed control and flutter compensation to be incorporated on replay. Reference frequencies as specified by IRIG<sup>16</sup> are usually adopted. These frequencies are generally used by manufacturers of analogue tape reproducers fitted with a fast response servo speed control. The frequencies are tabulated below.

| Tape Speed         | Compensation Tone Frequency |

|--------------------|-----------------------------|

| 60 ips             | 100 KHz                     |

| 30 ips             | 50 KHz                      |

| 15 ips             | 25 KHz                      |

| $7\frac{1}{2}$ ips | 12.5 KHz                    |

| $3\frac{3}{4}$ ips | 6·25 KHz                    |

| $1\frac{7}{8}$ ips | 3·125 KHz                   |

The reference frequency stability as laid down by IRIG is required to be better than 0.01%. To achieve such stability a crystal oscillator is required.

In a recording system which has been developed at these laboratories the reference frequencies tabulated above have been adopted. Further, clock signals for a digital data acquisition system at present under development (Sec. B2) are also required. It is intended that these clock frequencies also be derived from the same crystal oscillator providing the reference frequencies.

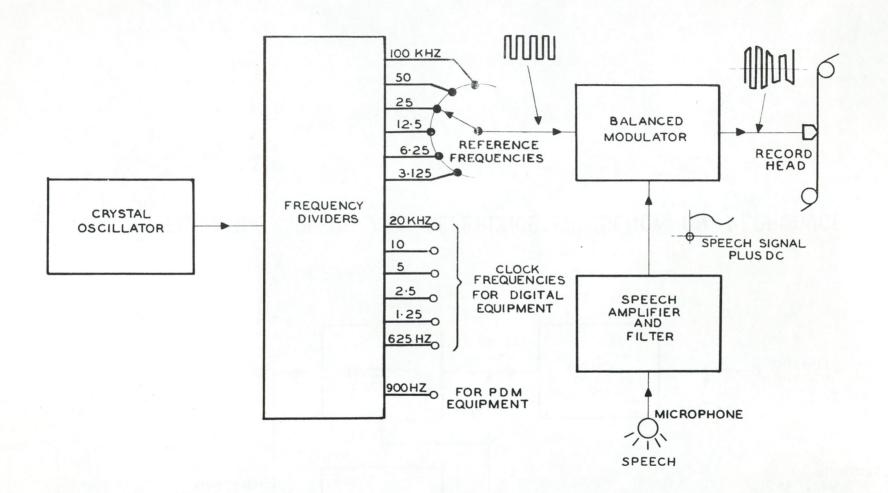

So that one record channel need not be completely taken up for the recording of reference frequencies it is desirable that speech and reference tones be recorded on a single direct record track. Card<sup>28</sup> has developed a crystal oscillator and suitable dividing circuits to obtain the

required reference frequencies. Further, using a balanced modulator, he records both reference frequency and speech on a single direct record track. A block diagram of the arrangement used for the recording is given in Fig. 7.

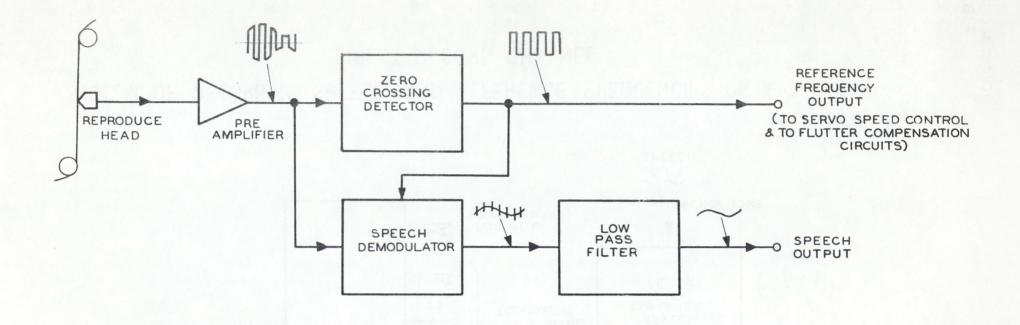

On replay the composite signal is passed through a zero crossing detector to provide the reference frequency output. The speech is separated using a suitable demodulator. The replay arrangement is depicted in block form in Fig. 8.

#### B1.2. Improvement in Signal to Noise Ratio in the FM Recording System

The accuracy of an FM recording system is largely dependent on the speed stability of both the record and the replay machines. Long term speed shifts between record and replay give rise to DC errors in the demodulated output. Alternating speed variations between record and replay give rise to an unwanted AC component or noise in the demodulated output. Athey<sup>29</sup> discusses the various causes which give rise to disturbances in tape motion and hence speed irregularities. Careful design of the tape transports greatly reduces these unwanted speed varitions.

Further improvement in the signal to noise ratio is possible using a servo speed control on replay. Such a system requires the recording of a stable reference frequency as described in Sec. B2.1. Assuming that the reference frequency is absolutely stable then any frequency changes appearing on replay will be due to speed variations between record and replay (neglecting any tape elongation or shrinkage between record and replay). Some years ago servo speed control was used only for maintaining the average replay speed equal to that for record. The standard practice was to record a 17 KHz or  $18 \cdot 24$ KHz carrier modulated by the 60 Hz (or other frequency) used to drive the capstan on record. On replay the 60 Hz signal was demodulated and used to control the frequency of the power source driving the reproduce capstan. More recently servos with a higher degree of sophistication have been introduced. These servos control the instantaneous rather than the average speed. Usually a 100 KHz signal or sub-multiple thereof is recorded to constitute the reference. Ampex Corporation provide such a system in their Model FR 1260 Recorder/Reproducer.

It is also possible to use the recorded reference frequency in a "flutter compensation" system. In such a system, compensation is applied by electronic circuits to reduce the effects of speed variations on the outputs of the FM reproduce channels. There are many problems associated with flutter compensation. To obtain an improved signal to noise ratio it is essential that the channel which is to be compensated is subject to exactly the same speed disturbances with regard to both amplitude and phase as the channel on which the reference frequency is recorded. The staggering of analogue heads makes this very difficult to achieve if the two channels in question belong to different head stacks. At the higher frequencies phase differences in the flutter even across the width of the tape can render the compensation useless.

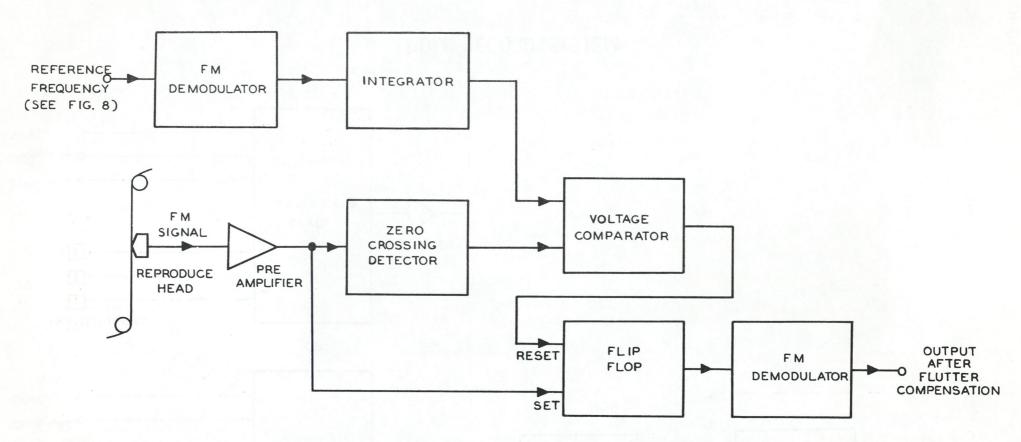

Some work has been done by Card<sup>28</sup> on a flutter compensation system which changes the area of the pulse appearing in the FM discriminator in sympathy with the variations in the reference signal frequency. The flutter compensation system is depicted in Fig. 9. Further work is required to ascertain whether any appreciable improvement occurs using flutter compensation in addition to the instantaneous servo speed control.

#### **B1.3. PDM System Requirements**

No multiplexing, de-keying or de-multiplexing equipment is presently available at these laboratories for use in the PDM system of recording.

Airborne PDM keyers are available at these laboratories for use in the PDM system of recording. The dynamic range of these keyers is variable from 310 to 610 microsecond and the minimum pulse duration from 60 to 170 microsecond. Ampex Corporation provides plug-in PDM record amplifiers which accept the PDM output from the above keyers and produce suitable drive currents for the record head fitted to their Model AR200 airborne tape recorder. Amplifiers of this type are available at these laboratories.

The precision with which the pulse durations can be recorded and reproduced is a function of tape speed. Some tests are required to provide this information.

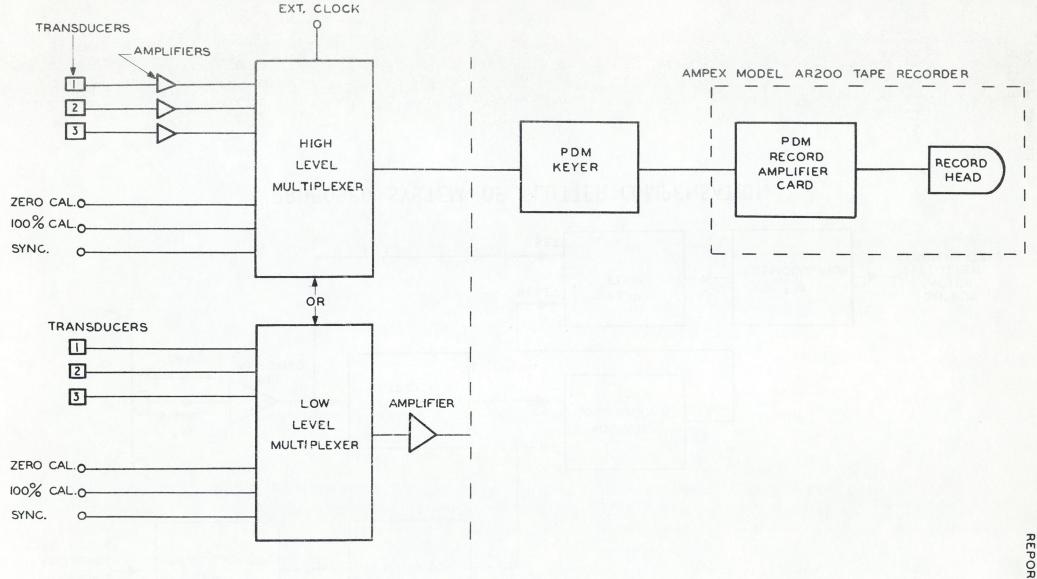

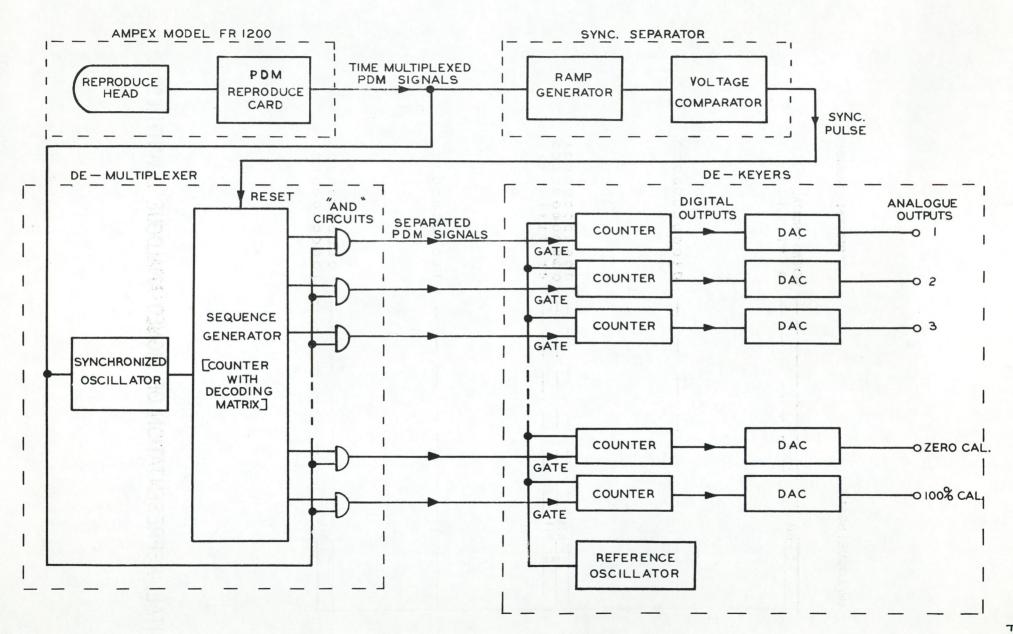

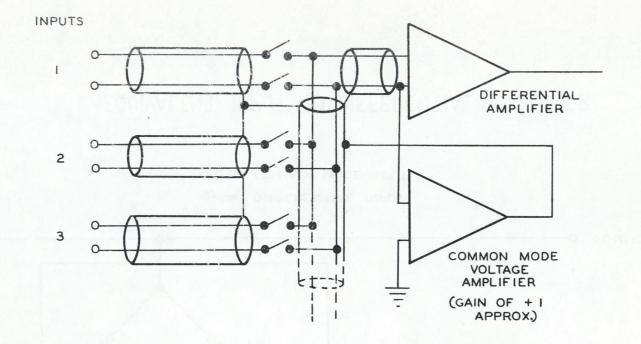

In Fig. 10 a block schema of a typical PDM recording system is illustrated. For a detailed description of a PDM recording system refer to Sec. A1.4. The signal level range required at the input of the keyer is typically 0 to 5 volts. Hence for many measurements pre-amplification

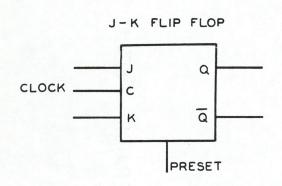

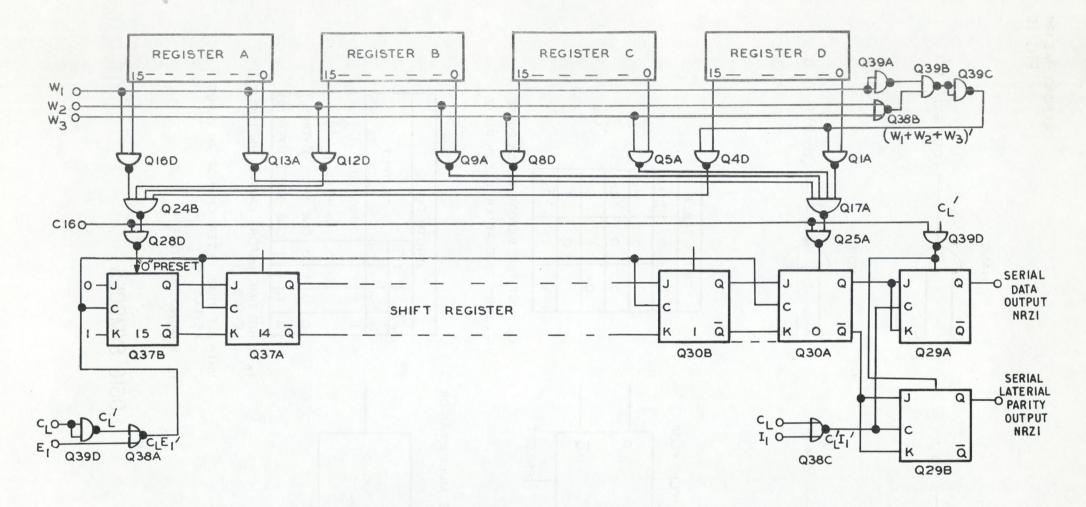

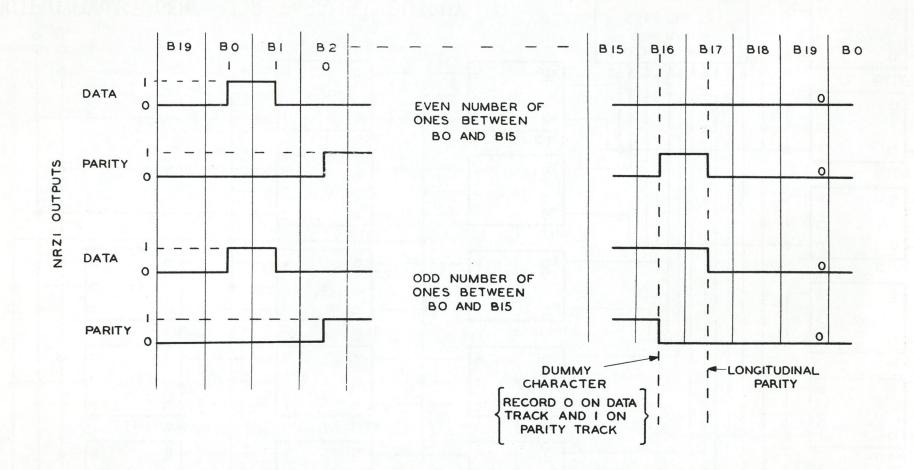

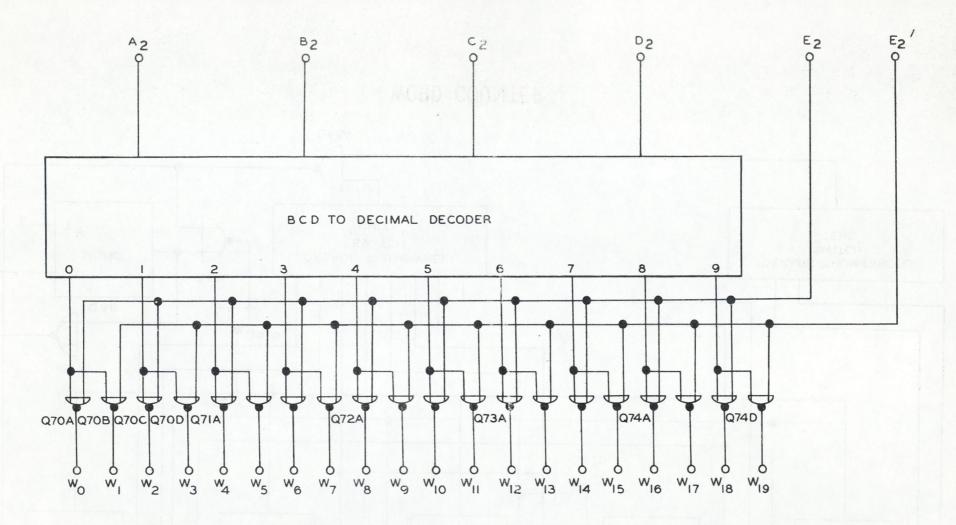

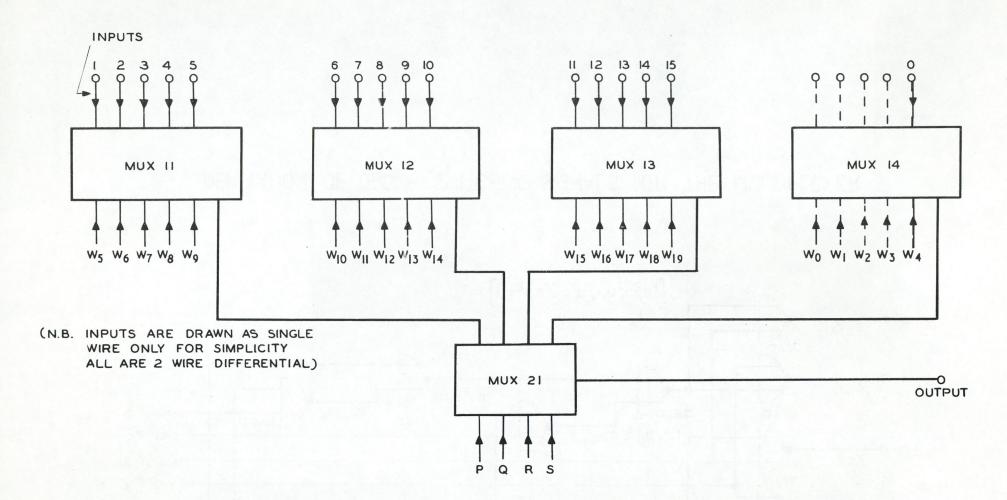

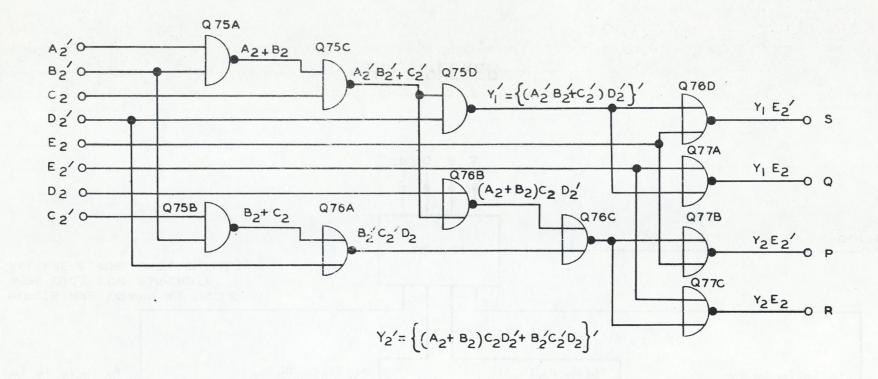

of signals is required. Signal pre-amplification may be performed either before or after the multiplexer. If pre-amplification is performed prior to the signals reaching the multiplexer then separate pre-amplifiers are required on each data channel. While this system is quite expensive because of the large amount of signal conditioning equipment required it has the advantage that the demands on the multiplexer are minimized. To achieve the 900 per second keying rate (as laid down by IRIG<sup>16</sup>) a solid state multiplexer is required. For high level multiplexing a single ended arrangement is adequate. If pre-amplification is performed after the multiplexer, a low level differential type of multiplexer is required. Very stringent accuracy requirements are placed on such a multiplexer particularly in view of the relatively large temperature range over which the equipment must perform. For more details on multiplexers refer to Sec. B2.4.1. It is envisaged that a 20 channel system will be adopted originally.